# With Extreme Scale Computing the Rules Have Changed

### **Jack Dongarra**

University of Tennessee Oak Ridge National Laboratory University of Manchester

**HPDC 2016 Achievement Award**

6/3/16

- Overview of High Performance Computing

- Look at some of the adjustments that are needed with Extreme Computing

## White House HPC Initiative

#### The White House

Office of the Press Secretary

For Immediate Release

July 29, 2015

#### Executive Order — Creating a National Strategic Computing Initiative

**EXECUTIVE ORDER**

-----

CREATING A NATIONAL STRATEGIC COMPUTING INITIATIVE

By the authority vested in me as President by the Constitution and the laws of the United States of America, and to maximize benefits of high-performance computing (HPC) research, development, and deployment, it is hereby ordered as follows:

Section 1. Policy. In order to maximize the benefits of HPC for economic competitiveness and scientific discovery, the United States Government must create a coordinated Federal strategy in HPC research, development, and deployment. Investment in HPC has contributed substantially to national economic prosperity and rapidly accelerated scientific discovery. Creating and deploying technology at the leading edge is vital to advancing my Administration's priorities and spurring innovation. Accordingly,

## **NSCI** has 5 Strategic Themes

- Create systems that can apply exaflops of computing power to exabytes of data.

- Keep the United States at the forefront of HPC capabilities.

- Improve HPC application developer productivity

- Make HPC readily available

- Establish hardware technology for future HPC systems.

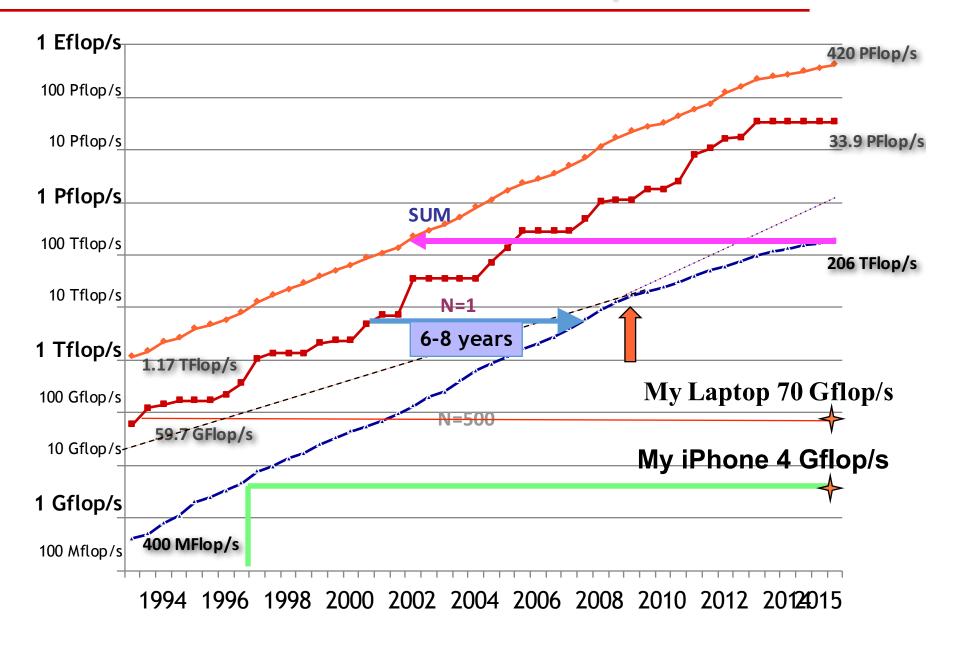

## State of Supercomputing Today

- Pflops (> 10<sup>15</sup> Flop/s) computing fully established with 81 systems.

- Three technology architecture possibilities or "swim lanes" are thriving.

- Commodity (e.g. Intel)

- Commodity + accelerator (e.g. GPUs) (104 systems)

- Special purpose lightweight cores (e.g. IBM BG, ARM, Intel's Knights Landing)

- Interest in supercomputing is now worldwide, and growing in many new markets (around 50% of Top500 computers are used in industry).

- Exascale (10<sup>18</sup> Flop/s) projects exist in many countries and regions.

- Intel processors have largest share, 89% followed by AMD, 4%.

#### H. Meuer, H. Simon, E. Strohmaier, & JD

- Listing of the 500 most powerful Computers in the World

- Yardstick: Rmax from LINPACK MPP

$$Ax=b$$

, dense problem

- All data available from www.top500.org

TPP performance

## Performance Development of HPC over the Last 24 Years from the Top500

# November 2015: The TOP 10 Systems

|      |                                                   |                                                                     |                        |           |                  |              |               | 1               |

|------|---------------------------------------------------|---------------------------------------------------------------------|------------------------|-----------|------------------|--------------|---------------|-----------------|

| Rank | Site                                              | Computer                                                            | Country                | Cores     | Rmax<br>[Pflops] | % of<br>Peak | Power<br>[MW] | MFlops<br>/Watt |

| 1    | National Super<br>Computer Center in<br>Guangzhou | Tianhe-2 NUDT,<br>Xeon 12C + IntelXeon Phi (57c)<br>+ Custom        | China                  | 3,120,000 | <i>33.9</i>      | 62           | 17.8          | 1905            |

| 2    | DOE / OS<br>Oak Ridge Nat Lab                     | Titan, Cray XK7, AMD (16C) +<br>Nvidia Kepler GPU (14c) +<br>Custom | USA                    | 560,640   | 17.6             | 65           | 8.3           | 2120            |

| 3    | DOE / NNSA<br>L Livermore Nat Lab                 | Sequoia, BlueGene/Q (16c)<br>+ custom                               | USA<br>STEELER STEELER | 1,572,864 | 17.2             | 85           | 7.9           | 2063            |

| 4    | RIKEN Advanced<br>Inst for Comp Sci               | K computer Fujitsu SPARC64<br>VIIIf×(8c) + Custom                   | Japan                  | 705,024   | 10.5             | 93           | 12.7          | 827             |

| 5    | DOE / OS<br>Argonne Nat Lab                       | Mira, BlueGene/Q (16c)<br>+ Custom                                  | USA                    | 786,432   | 8.16             | 85           | 3.95          | 2066            |

| 6    | DOE / NNSA /<br>Los Alamos & Sandia               | Trinity, Cray XC40,Xeon 16C +<br>Custom                             | USA                    | 301,056   | 8.10             | 80           |               |                 |

| 7    | Swiss CSCS                                        | Piz Daint, Cray XC30, Xeon 8C +<br>Nvidia Kepler (14c) + Custom     | Swiss                  | 115,984   | 6.27             | 81           | 2.3           | 2726            |

| 8    | HLRS Stuttgart                                    | Hazel Hen, Cray XC40, Xeon<br>12C+ Custom                           | Germany                | 185,088   | 5.64             | 76           |               |                 |

| 9    | KAUST                                             | Shaheen II, Cray XC40, Xeon<br>16C + Custom                         | Saudi<br>Arabia        | 196,608   | 5.54             | 77           | 2.8           | 1954            |

| 10   | Texas Advanced<br>Computing Center                | Stampede, Dell Intel (8c) + Intel<br>Xeon Phi (61c) + IB            | USA                    | 204,900   | 5.17             | 61           | 4.5           | 1489            |

500 (368) Karlsruher

MEGAWARE Intel

Germany

10,800

.206

95

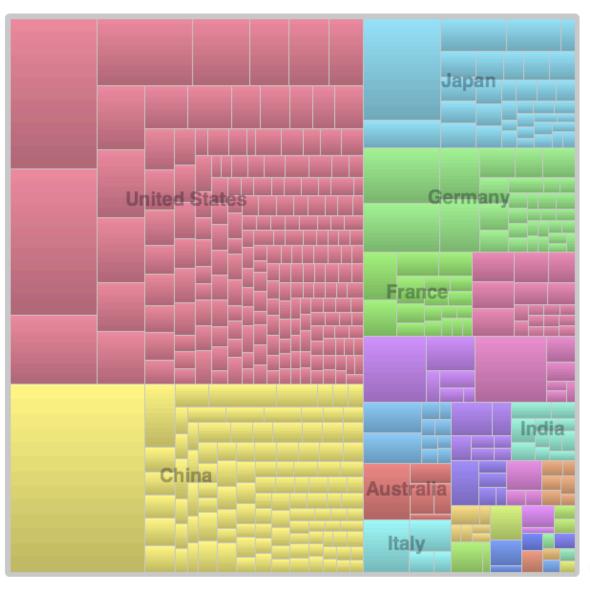

## **Countries Share**

**Absolute Counts**

US: 201 China: 109 Japan: 37 UK: 18 France: 18 Germany: 32

China nearly tripled the number of systems on the latest list, while the number of systems in the US has fallen to the lowest point since the TOP500 list was created.

## Recent Developments

- US DOE planning to deploy O(100) Pflop/s systems for 2017-2018 \$525M hardware

- Oak Ridge Lab and Lawrence Livermore Lab to receive IBM and Nvidia based systems

- Argonne Lab to receive Intel based system

- > After this the Exaflop

## Since the Dept of Commerce Action ...

- Expanded focus on Chinese made HW and SW

- Anything but from the US

- Three separate developments in HPC

- Wuxi

- Sunway TaihuLight 125 Pflops Peak, all Chinese, ShenWei Proc, June 2016 (ISC2016)

- NUDT

- Tianhe-2A O(100) Pflops will be Chinese ARM, 2017

- · CAS ICT

- Godson MIPS and new processors

- In the latest "5 Year Plan"

- Govt push to build out a domestic HPC ecosystem.

- Exascale system, will not use any US chips

- Targeting China's key industrial apps, via SW 6/3/16 renters.

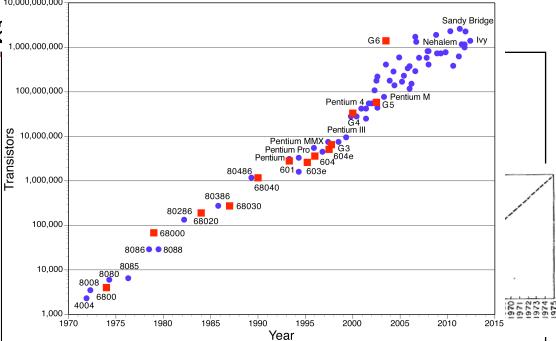

## Technology Trends:

Microprocessor Ca.

Gordon Moore (co-founder of Intel) Electronics Magazine, 1965 Number of devices/chip doubles every 18 months

2X transistors/Chip Every

1.5 years

Called "Moore's Law"

The future of integrated electronics is the future of electronics itself. The advantages of integration will bring about a proliferation of electronics, pushing this science into many new areas.

Integrated circuits will lead to such wonders as home computers—or at least terminals connected to a central computer—automatic controls for automobiles, and personal portable communications equipment. The electronic wristwatch needs only a display to be feasible today.

But the biggest potential lies in the production of large systems. In telephone communications, integrated circuits in digital filters will separate channels on multiplex equipment. Integrated circuits will also switch telephone circuits and perform data processing.

Computers will be more powerful, and will be organized in completely different ways. For example, memories built of integrated electronics may be distributed throughout the

#### The author

Dr. Gordon E. Moore is one of the new breed of electronic engineers, schooled in the physical sciences rather than in electronics. He earned a B.S. degree in chemistry from the machine instead of being concentrated in a central unit. In addition, the improved reliability made possible by integrated circuits will allow the construction of larger processing units. Machines similar to those in existence today will be built at lower costs and with faster turn-around.

#### Present and future

By integrated electronics, I mean all the various technologies which are referred to as microelectronics today as well as any additional ones that result in electronics functions supplied to the user as irreducible units. These technologies were first investigated in the late 1950's. The object was to miniaturize electronics equipment to include increasingly complex electronic functions in limited space with minimum weight. Several approaches evolved, including microassembly techniques for individual components, thinfilm structures and semiconductor integrated circuits.

Each approach evolved rapidly and converged so that each borrowed techniques from another. Many researchers believe the way of the future to be a combination of the various approaches.

The advocates of semiconductor integrated circuitry are already using the improved characteristics of thin-film resistors by applying such films directly to an active semiconductor substrate. Those advocating a technology based upon

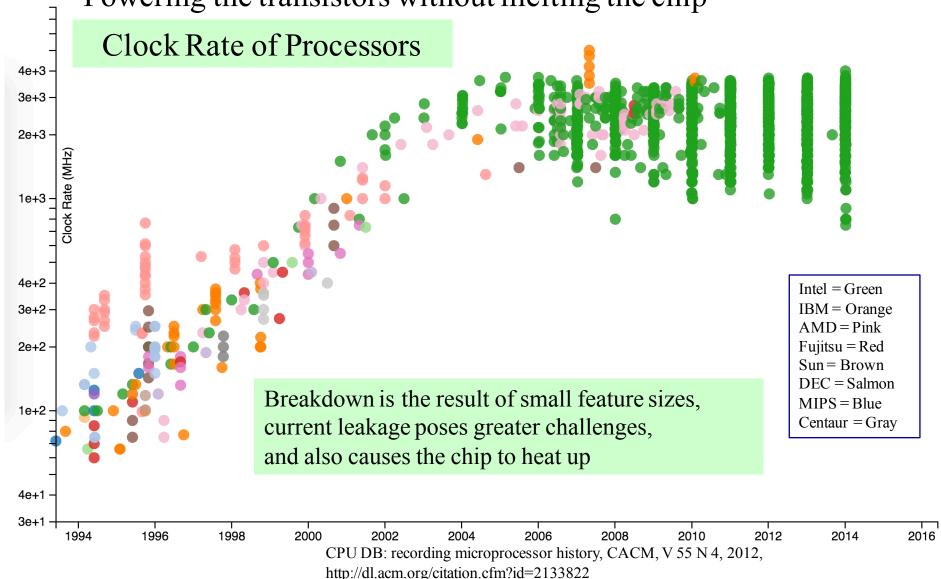

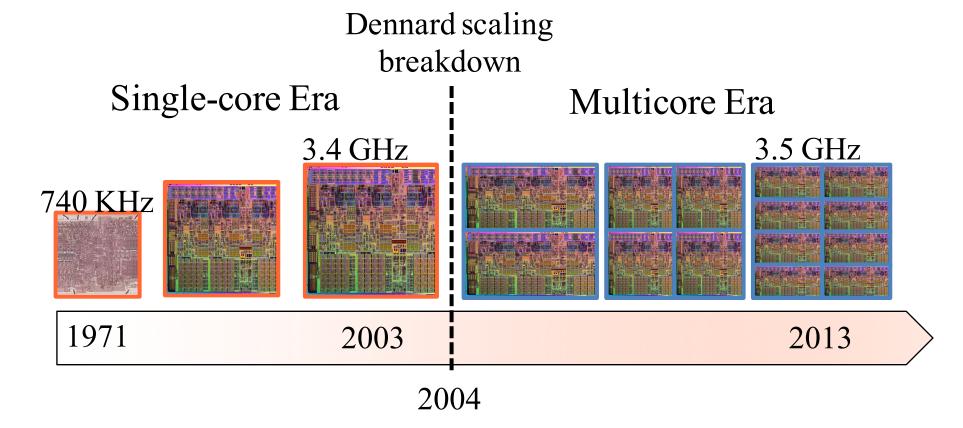

## Moore's Secret Sauce: Dennard Scaling

Moore's Law put lots more transistors on a chip...but it's Dennard's Law that made them useful

Dennard observed that voltage and current should be proportional to the linear dimensions of a transistor

#### Dennard Scaling:

- Decrease feature size by a factor of  $\lambda$  and decrease voltage by a factor of  $\lambda$ ; then

- # transistors increase by  $\lambda^2$

- Clock speed increases by  $\lambda$

- Energy consumption does not change

2x transistor count 40% faster 50% more efficient

#### Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions

ROBERT H. DENNARD, MEMBEB, IEEE, FRITZ H. GAENSSLEN, HWA-NIEN YU, MEMBEB, IEEE, V. LEO RIDEOUT, MEMBER, IEEE, ERNEST BASSOUS, AND ANDRE R. LEBLANC, MEMBER, IEEE

Abstract—This paper considers the design, fabrication, and characterization of very small MOSFET switching devices suitable for digital integrated circuits using dimensions of the order of 1 µ. Scaling relationships are presented which show how a conventional MOSFET can be reduced in size. An improved small device structure is presented that uses ion implantation to provide shallow source and drain regions and a nonuniform substrate doping profile. One-dimensional models are used to predict the substrate doping grofile and the corresponding threshold voltage versus source voltage characteristic. A two-dimensional current transport model is used to predict the relative degree of short-channel effects for different device parameter combinations. Polysikion-gate MOSFET's with channel lengths as short as O.5 µ were fabricated, and the device characteristics measured and compared with predicted values. The performance improvement expected from using these very small devices in highly miniaturized integrated circuits is projected.

Manuscript received May 20, 1974; revised July 3, 1974. The authors are with the IBM T. J. Watson Research Center Yorktown Heights, N.Y. 10598. LIST OF SYMBOLS

A Inverse semilogarithmic slope of subthreshold characteristic.

D Width of idealized step function profile for channel implant.  $\Delta W_t$  Work function difference between gate and substrate.

Dielectric constants for silicon and silicon dioxide.

L Drain current.

E Boltzmann's constant.

K Unitless scaling constant.

L MOSFET channel length.  $\mu_{tft}$  Effective surface mobility.

In Intrinsic carrier concentration.

Substrate acceptor concentration. Band bending in silicon at the onset of

strong inversion for zero substrate

[Dennard, Gaensslen, Yu, Rideout, Bassous, Leblanc, IEEE JSSC, 1974] 13

# Unfortunately Dennard Scaling is Over: What is the Catch?

Powering the transistors without melting the chip

## Dennard Scaling Over

### Evolution of processors

The primary reason cited for the breakdown is that at small sizes, current leakage poses greater challenges, and also causes the chip to heat up, which creates a threat of thermal runaway and therefore further increases energy costs. Can't continue to reduce the cycle time.

## **High Cost of Data Movement**

| Operation                | Energy<br>consumed | Time<br>needed |

|--------------------------|--------------------|----------------|

| 64-bit multiply-add      | 200 pJ             | 1 nsec         |

| Read 64 bits from cache  | 800 pJ             | 3 nsec         |

| Move 64 bits across chip | 2000 pJ            | 5 nsec         |

| Execute an instruction   | 7500 pJ            | 1 nsec         |

| Read 64 bits from DRAM   | 12000 pJ           | 70 nsec        |

Communication is now almost all of the parts cost, almost all of the time spent, and almost all of the energy and power consumed!

## Peak Performance - Per Core

$FLOPS = cores \times clock \times$

#### Floating point operations per cycle per core

- ★ Most of the recent computers have FMA (Fused multiple add): (i.e. x ←x + y\*z in one cycle)

- + Intel Xeon earlier models and AMD Opteron have SSE2

- + 2 flops/cycle DP & 4 flops/cycle SP

- + Intel Xeon Nehalem ('09) & Westmere ('10) have SSE4

- + 4 flops/cycle DP & 8 flops/cycle SP

- + Intel Xeon Sandy Bridge('11) & Ivy Bridge ('12) have AVX

- + 8 flops/cycle DP & 16 flops/cycle SP

- + IntelXeon Haswell ('13) & (Broadwell ('14)) AVX2

- + 16 flops/cycle DP & 32 flops/cycle SP

- + Xeon Phi (per core) is at 16 flops/cycle DP & 32 flops/cycle SP

- + Intel Xeon Skylake (server) AVX 512

- + 32 flops/cycle DP & 64 flops/cycle SP

- + Knight's Landing

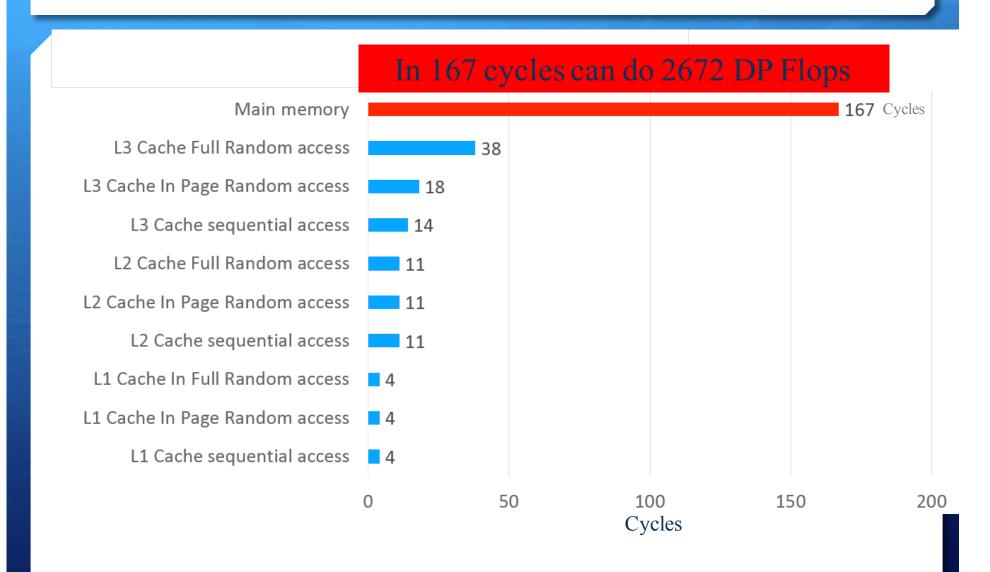

## CPU Access Latencies in Clock Cycles

# Classical Analysis of Algorithms May Not be Valid

- Processors over provisioned for floating point arithmetic

- Data movement extremely expensive

- Operation count is not a good indicator of the time to solve a problem.

- Algorithms that do more ops may actually take less time.

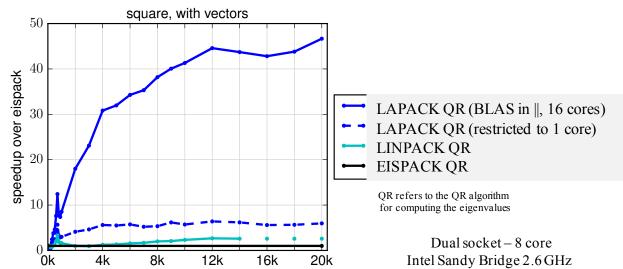

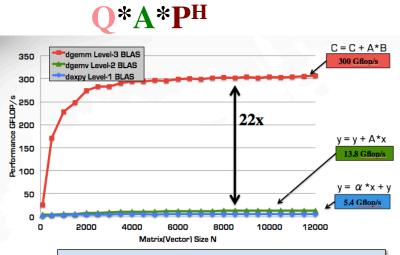

## Singular Value Decomposition

Level 1, 2, & 3 BLAS

columns (matrix size  $N \times N$ )

(8 Flops per core per cycle)

#### 3 Generations of software compared

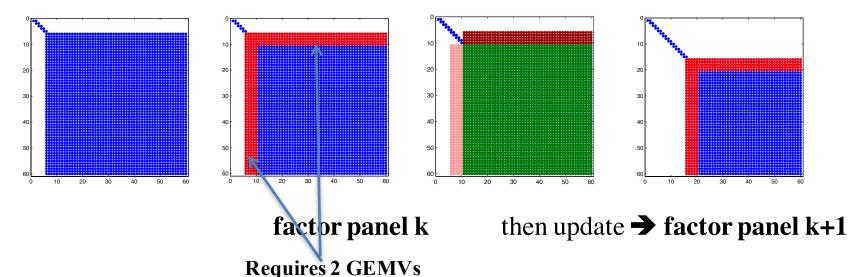

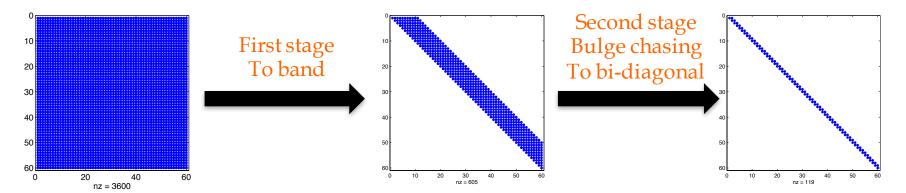

# Bottleneck in the Bidiagonalization The Standard Bidiagonal Reduction: xGEBRD

Two Steps: Factor Panel & Update Tailing Matrix

#### **\*** Characteristics

- Total cost  $8n^3/3$ , (reduction to bi-diag

- Too many Level 2 BLAS operations

- 4/3 n<sup>3</sup> from GEMV and 4/3 n<sup>3</sup> from G

- Performance limited to 2\* performan

- →Memory bound algorithm.

16 cores Intel Sandy Bridge, 2.6 GHz, 20 MB shared L3 cache. The theoretical peak per core double precision is 20.4 Gflop/s per core. Compiled with icc and using MKL 2015.3.187

#### **Recent Work on 2-Stage Algorithm**

#### **\*** Characteristics

- **Stage 1:**

- Fully Level 3 BLAS

- Dataflow Asynchronous execution

- **Stage 2:**

- Level "BLAS-1.5"

- Asynchronous execution

- Cache friendly kernel (reduced communication)

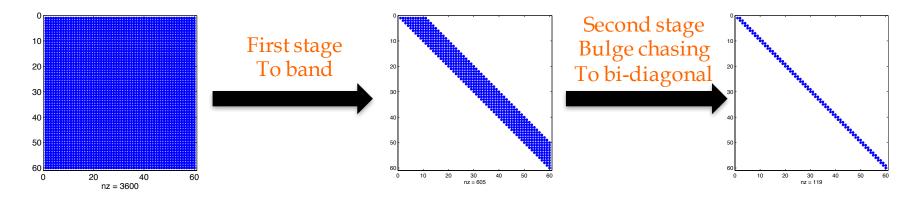

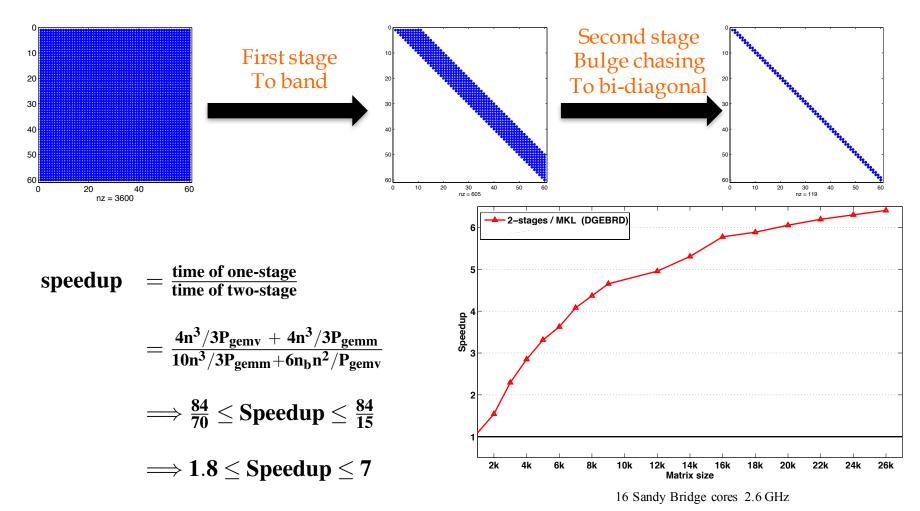

#### Recent work on developing new 2-stage algorithm

$$\begin{split} \text{flops} & \approx \frac{\sum\limits_{s=1}^{\frac{n-n_b}{n_b}} 2n_b^3 + (nt-s)3n_b^3 + (nt-s)\frac{10}{3}n_b^3 + (nt-s)\times (nt-s)5n_b^3 \\ & + \sum\limits_{s=1}^{\frac{n-n_b}{n_b}} 2n_b^3 + (nt-s-1)3n_b^3 + (nt-s-1)\frac{10}{3}n_b^3 + (nt-s)\times (nt-s-1)5n_b^3 \\ & \approx \frac{10}{3}n^3 + \frac{10n_b}{3}n^2 + \frac{2n_b}{3}n^3 \\ & \approx \frac{10}{3}n^3(\text{gemm})_{first \, stage} \end{split} \qquad \qquad \text{flops} \quad = 6\times n_b \times n^2(\text{gemv})_{second \, stage} \end{split}$$

More Flops, original did 8/3 n<sup>3</sup> 25% More flops

#### Recent work on developing new 2-stage algorithm

if  $P_{gemm}$  is about 22x  $P_{gemv}$  and  $120 \le n_b \le 240$ .

25% More flops and 1.8 – 7 times faster

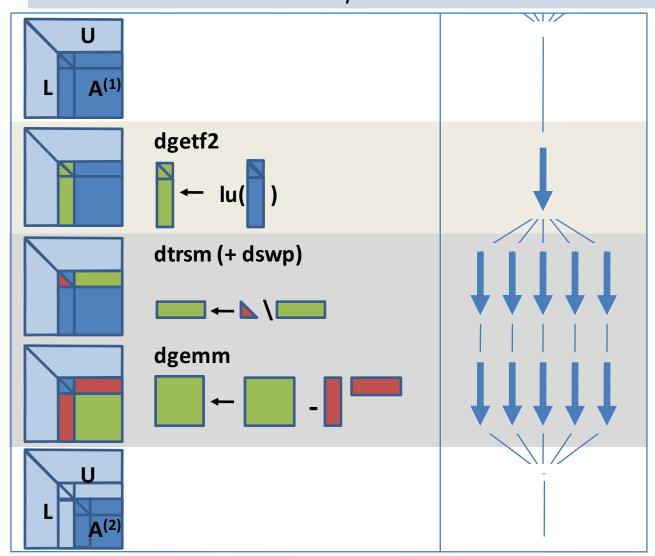

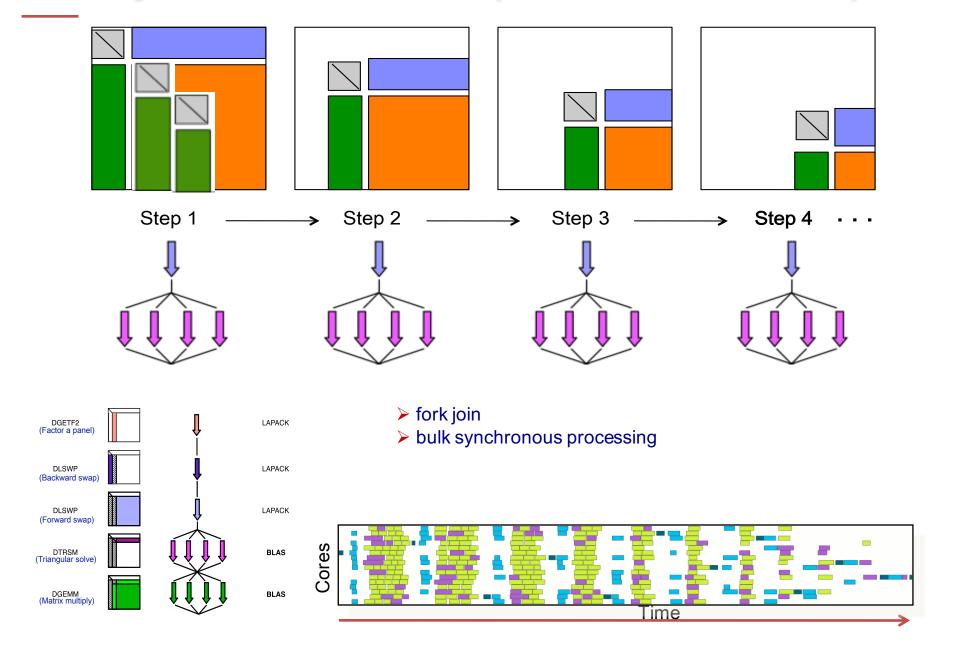

#### Parallelization of LU and QR.

#### Parallelize the update:

- Easy and done in any reasonable software.

- This is the 2/3n³ term in the FLOPs count.

- · Can be done efficiently with LAPACK+multithreaded BLAS

Fork - Join parallelism Bulk Sync Processing

dgemm

# Synchronization (in LAPACK LU)

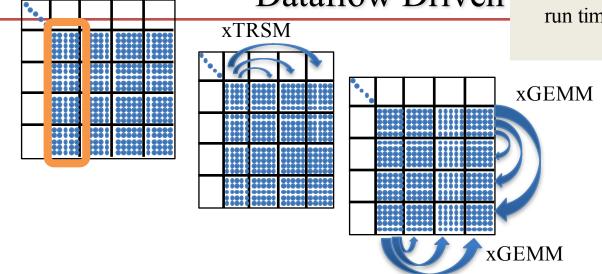

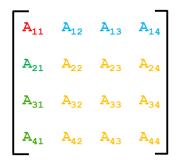

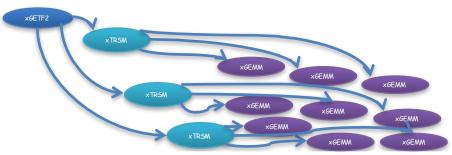

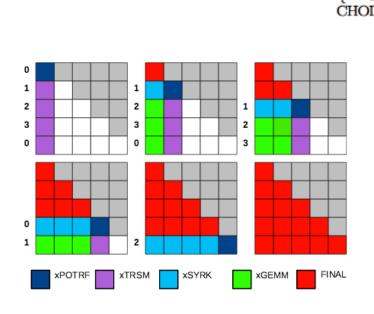

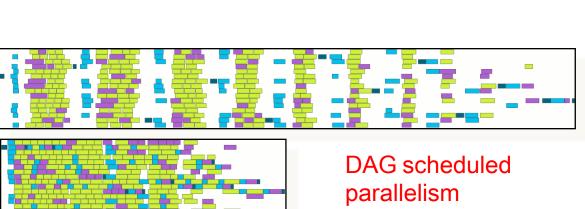

## PLASMA LU Factorization

#### Dataflow Driven

Numerical program generates tasks and run time system executes tasks respecting data dependences.

#### **Sparse / Dense Matrix System**

#### **DAG-based factorization**

**Updates (Schur complement)** GEMMs, SYRKs, TRMMs

And many other BLAS/LAPACK, e.g., for application specific solvers, preconditioners, and matrices

## OpenMP tasking

- Added with OpenMP 3.0 (2009)

- Allows parallelization of irregular problems

- OpenMP 4.0 (2013) Tasks can have dependencies

- DAGs

## **Tiled Cholesky Decomposition**

```

#pragma omp parallel

#pragma omp master

CHOLESKY(A); }

CHOLESKY(A) {

for (k = 0; k < M; k++) {

#pragma omp task depend(inout:A(k,k)[0:tilesize]

POTRF(A(k,k)); }

for (m = k+1; m < M; m++) {

#pragma omp task \

depend(in:A(k,k)[0:tilesize]) \

depend (inout: A(m, k) [0: tilesize])

{ TRSM(A(k,k),A(m,k)); }

for (m = k+1; m < M; m++) {

#pragma omp task \

depend(in:A(m,k)[0:tilesize]) \

depend (inout: A(m,m) [0: tilesize])

\{ SYRK(A(m,k),A(m,m)); \}

for (n = k+1; n < m; n++)

#pragma omp task \

depend(in:A(m,k)[0:tilesize],

A(n,k)[0:tilesize]

depend(inout:A(m,n)[0:tilesize])

\{GEMM(A(m,k),A(n,k),A(m,n));\}

}

```

Cores

## Dataflow Based Design

#### **Objectives**

- > High utilization of each core

- > Scaling to large number of cores

- > Synchronization reducing algorithms

#### Methodology

- Dynamic DAG scheduling

- > Explicit parallelism

- > Implicit communication

- > Fine granularity / block data layout

SArbitrary DAG with dynamic scheduling

Fork-join parallelism Notice the synchronization penalty in the presence of heterogeneity.

# Avoiding Synchronization

- "Responsibly Reckless" Algorithms

- Try fast algorithm (unstable algorithm) that might fail (but rarely)

- Check for instability

- · If needed, recompute with stable algorithm

#### Introduction

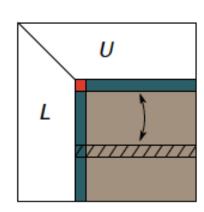

#### LU decomposition (Gaussian Elimination) for the solution of Ax = b

for

$$k=1$$

to  $n$  do

$$a_{k+1:n,k} \leftarrow \frac{a_{k+1:n,k}}{a_{kk}}$$

$$a_{k+1:n,k+1:n} \leftarrow a_{k+1:n,k+1:n} - a_{k+1:n,k} \times a_{k,k+1:n}$$

end for

- Stability issue: a<sub>kk</sub> may be small or zero ⇒ large element growth ⇒ elements of normal size lost in summation.

- Partial pivoting (GEPP): swap rows so that each  $a_{kk}$  is large. row k is exchanged with row p such that  $|a_{pk}| = \max_{\substack{j \ge k}} |a_{jk}|$  Eventually, PA = LU (P permutation matrix).

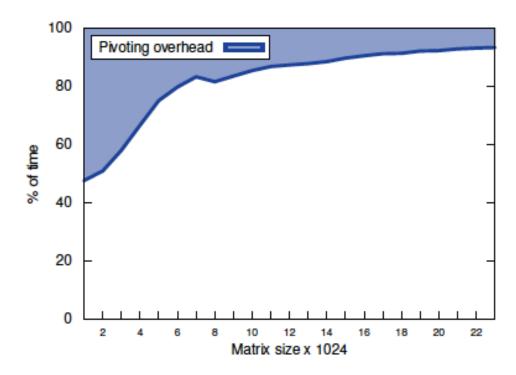

## Pivoting is expensive

- Complete pivoting, partial pivoting, tournament pivoting, etc.

- GEPP implemented in most numerical libraries (LAPACK...)

- No floating point operation in pivoting but it involves irregular movements of data

- Communication overhead due to pivoting:  $O(n^2)$  comparisons

Cost of partial pivoting in LU factorization (MAGMA), Nvidia Kepler K20

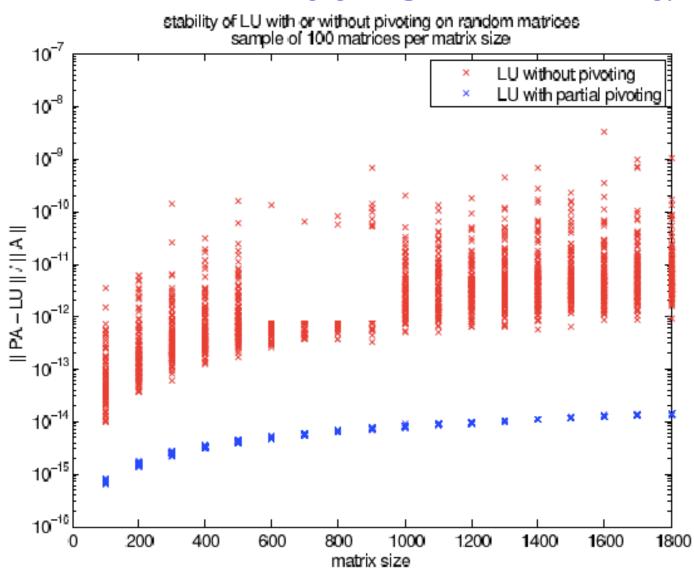

#### Random matrices are nice (for pivoting)

(see [ Trefethen and Schreiber, SIMAX 90 ], [ Yeung and Chan, SIMAX 97 ])

### How to remove pivoting

#### No pivoting by randomizing instead:

- For general systems (LU factorization):

Initially proposed by [ Parker, 1995 ]

Revisited in [ MB, Dongarra, Herrmann Tomov, TOMS 2013 ]

- Idea: the original matrix is transformed into a matrix that would be sufficiently "random" so that, with a probability close to 1, pivoting is not needed.

### How to avoid pivoting with randomization?

#### Random Butterfly Transformation (RBT)

$$Ax = b \equiv \underbrace{U^T AV}_{A_r} \underbrace{V^{-1} x}_{y} = \underbrace{U^T b}_{c}$$

- Compute  $A_r = U^T A V$  with U, V random (recursive butterflies)

- Factorize A<sub>r</sub> without pivoting (GENP)

- Solve  $A_r y = U^T b$  then x = V y

#### Requirements:

- Randomization must be cheap

- Fast GENP ("Cholesky" speed)

- Accuracy close to that of GEPP (possibly IR)

### **Butterfly Matrix**

A **butterfly matrix** is defined as any *n*-by-*n* matrix of the form:

$$B = \frac{1}{\sqrt{2}} \begin{pmatrix} R & S \\ R & -S \end{pmatrix}$$

where R and S are random diagonal matrices.

$$B = \left(\begin{array}{c} \\ \\ \end{array}\right)$$

Remark:

$$B = \frac{1}{\sqrt{2}} \begin{pmatrix} I_{n/2} & I_{n/2} \\ I_{n/2} & -I_{n/2} \end{pmatrix} \begin{pmatrix} R & 0 \\ 0 & S \end{pmatrix}$$

#### Numerical issues

#### Stability of RBT?

- "Average" growth factor expressed in [ Parker, 95 ]

- Iterative refinement is systematically added

```

1: r_k \leftarrow b - Ax_{k-1}

```

2: solve  $Ly = r_k$

3: solve  $Uz_k = y$

4:  $X_k \leftarrow X_{k-1} + Z_k$

check convergence

- Backward error (available from IR process) is sent back

- Future work: probabilistic error bounds

### Tests on accuracy

| Matrix     | Cond                 | GENP                     | GEPP                     | QR                       | RBT                      | REC | IR |

|------------|----------------------|--------------------------|--------------------------|--------------------------|--------------------------|-----|----|

| augment    | 4 · 10 <sup>4</sup>  | 1.28 · 10 <sup>-14</sup> | 2.28 · 10 <sup>-15</sup> | 2.99 · 10 <sup>-16</sup> | 2.81 · 10 <sup>-16</sup> | 1   | 1  |

| gfpp       | 5 · 10 <sup>2</sup>  | 9.01 · 10 <sup>-01</sup> | 6.88 · 10 <sup>-01</sup> | 1.06 · 10 <sup>-16</sup> | 1.27 · 10 <sup>-16</sup> | 1   | 1  |

| chebspec   | 2 · 10 <sup>14</sup> | 1.19 · 10 <sup>-15</sup> | 3.29 · 10 <sup>-16</sup> | 5.22 · 10 <sup>-15</sup> | 3.23 · 10 <sup>-14</sup> | 1   | 0  |

| circul     | 1 · 10 <sup>3</sup>  | 1.74 · 10 <sup>-13</sup> | 1.66 · 10 <sup>-15</sup> | 2.66 · 10 <sup>-15</sup> | 2.66 · 10 <sup>-15</sup> | 1   | 0  |

| condex     | 1 · 10 <sup>2</sup>  | 7.32 · 10 <sup>-15</sup> | 5.98 · 10 <sup>-15</sup> | 8.34 · 10 <sup>-15</sup> | 6.50 · 10 <sup>-15</sup> | 1   | 0  |

| fiedler    | 7 · 10 <sup>5</sup>  | Fail                     | 2.11 · 10 <sup>-15</sup> | 1.54 · 10 <sup>-14</sup> | 7.90 · 10 <sup>-15</sup> | 1   | 0  |

| Hadamard   | 1 · 10 <sup>0</sup>  | 0 · 10 <sup>0</sup>      | 0 · 10 <sup>0</sup>      | 7.58 · 10 <sup>-16</sup> | 8.33 · 10 <sup>-15</sup> | 1   | 0  |

| normaldata | 3 · 10 <sup>4</sup>  | 2.03 · 10 <sup>-12</sup> | 6.30 · 10 <sup>-15</sup> | 2.38 · 10 <sup>-16</sup> | 3.30 · 10 <sup>-16</sup> | 1   | 1  |

| orthog     | 1 · 10 <sup>0</sup>  | 5.64 · 10 <sup>-01</sup> | 4.33 · 10 <sup>-15</sup> | 3.70 · 10 <sup>-16</sup> | 4.31 · 10 <sup>-16</sup> | 2   | 1  |

| randcorr   | 3 · 10 <sup>3</sup>  | 5.12 · 10 <sup>-16</sup> | 4.04 · 10 <sup>-16</sup> | 5.73 · 10 <sup>-16</sup> | 5.92 · 10 <sup>-16</sup> | 1   | 0  |

| toeppd     | 7 · 10 <sup>5</sup>  | 2.53 · 10 <sup>-13</sup> | 2.60 · 10 <sup>-15</sup> | 8.39 · 10 <sup>-15</sup> | 5.71 · 10 <sup>-15</sup> | 1   | 0  |

| Foster     | 5 · 10 <sup>2</sup>  | 1 · 10 <sup>0</sup>      | 1 · 10 <sup>0</sup>      | 1.90 · 10 <sup>-16</sup> | 3.30 · 10 <sup>-16</sup> | 2   | 1  |

| [-1,1]     | 2 · 10 <sup>3</sup>  | 2.19 · 10 <sup>-11</sup> | 5.19 · 10 <sup>-15</sup> | 2.33 · 10 <sup>-16</sup> | 2.35 · 10 <sup>-16</sup> | 1   | 1  |

| [0, 1]     | 4 · 10 <sup>4</sup>  | 1.97 · 10 <sup>-12</sup> | 2.85 · 10 <sup>-15</sup> | 2.15 · 10 <sup>-15</sup> | 1.79 · 10 <sup>-15</sup> | 1   | 1  |

| {-1,1}     | 4 · 10 <sup>3</sup>  | Fail                     | 3.96 · 10 <sup>-15</sup> | 2.38 · 10 <sup>-16</sup> | 2.70 · 10 <sup>-16</sup> | 2   | 1  |

| {0, 1}     | 5 · 10 <sup>4</sup>  | Fail                     | 4.39 · 10 <sup>-15</sup> | 2.19 · 10 <sup>-15</sup> | 1.09 · 10 <sup>-15</sup> | 2   | 1  |

| Turing     | 5 · 10 <sup>19</sup> | 0 · 10 <sup>0</sup>      | 0 · 10 <sup>0</sup>      | 7.16 · 10 <sup>-13</sup> | 1.05 · 10 <sup>-14</sup> | 2   | 1  |

| i-j        | 7 · 10 <sup>5</sup>  | Fail                     | 3.33 · 10 <sup>-16</sup> | 1.54 · 10 <sup>-14</sup> | 6.05 · 10 <sup>-15</sup> | 1   | 0  |

| max(i,j)   | 3 · 10 <sup>6</sup>  | 2.16 · 10 <sup>-14</sup> | 1.21 · 10 <sup>-15</sup> | 1.46 · 10 <sup>-14</sup> | 2.27 · 10 <sup>-15</sup> | 1   | 1  |

Componentwise backward error (n = 1024, tile size=8)

$$\omega = \max_i \frac{|Ax - b|_i}{(|A| \cdot |x| + |b|)_i}$$

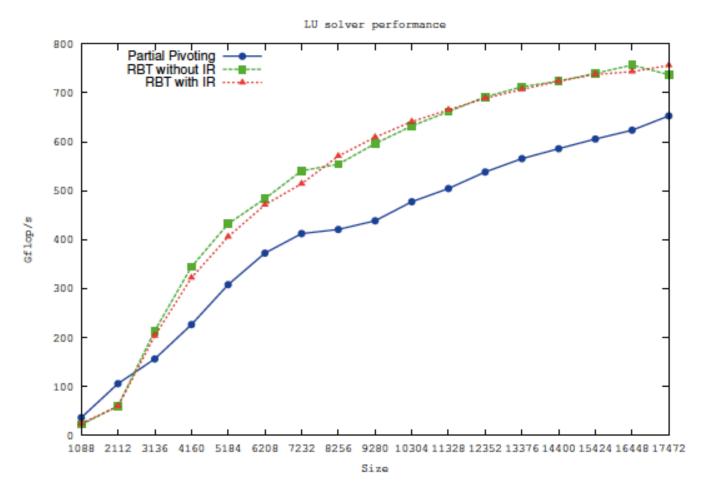

#### Performance on GPU

Performance on 12 Intel Xeon X5680 cores + 1 Nvidia Kepler K20 Using same number of flops used for each implementation.

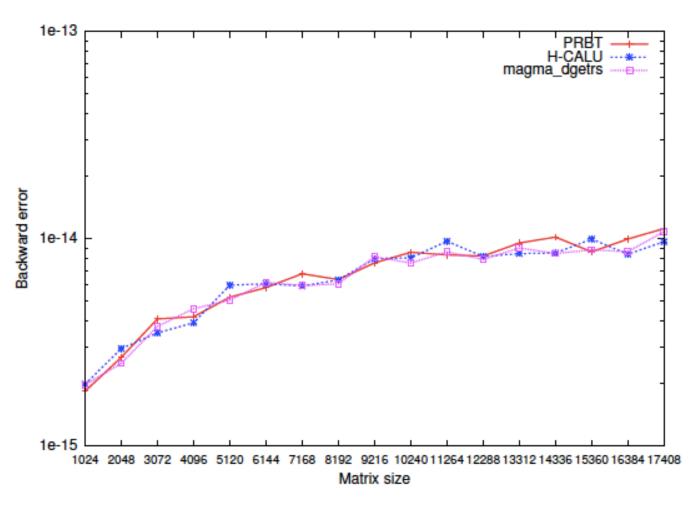

### RBT vs other solvers (accuracy)

Comparison of componentwise backward error (double precision)

# Mixed Precision Methods

- Mixed precision, use the lowest precision required to achieve a given accuracy outcome

- Improves runtime, reduce power consumption, lower data movement

- Reformulate to find correction to solution, rather than solution; Δx rather than x.

$$x_{i+1} = x_i - \frac{f(x_i)}{f'(x_i)}$$

$$x_{i+1} - x_i = -\frac{f(x_i)}{f'(x_i)} 42$$

## Idea Goes Something Like This...

- Exploit 32 bit floating point as much as possible.

- Especially for the bulk of the computation

- Correct or update the solution with selective use of 64 bit floating point to provide a refined results

- Intuitively:

- Compute a 32 bit result,

- Calculate a correction to 32 bit result using selected higher precision and,

- Perform the update of the 32 bit results with the correction using high precision.

# Mixed-Precision Iterative Refinement

Iterative refinement for dense systems, Ax = b, can work this way.

```

LU = lu(A)

O(n^3)

O(n^2)

x = L\setminus(U\setminus b)

O(n^2)

r = b - Ax

WHILE || r || not small enough

z = L \setminus (U \setminus r)

O(n^2)

O(n^1)

X = X + Z

O(n^2)

r = b - Ax

END

```

Wilkinson, Moler, Stewart, & Higham provide error bound for SP fl pt results when using DP fl pt.

# Mixed-Precision Iterative Refinement

Iterative refinement for dense systems, Ax = b, can work this way.

```

O(n^3)

LU = lu(A)

SINGLE

O(n^2)

x = L\setminus(U\setminus b)

SINGLE

O(n^2)

r = b - Ax

DOUBLE

WHILE || r || not small enough

z = L \setminus (U \setminus r)

SINGLE

O(n^2)

O(n^1)

DOUBLE

X = X + Z

r = b - Ax

O(n^2)

DOUBLE

END

```

- Wilkinson, Moler, Stewart, & Higham provide error bound for SP fl pt results when using DP fl pt.

- It can be shown that using this approach we can compute the solution to 64-bit floating point precision.

- Requires extra storage, total is 1.5 times normal;

- O(n³) work is done in lower precision

- O(n²) work is done in high precision

- Problems if the matrix is ill-conditioned in sp; O(108)

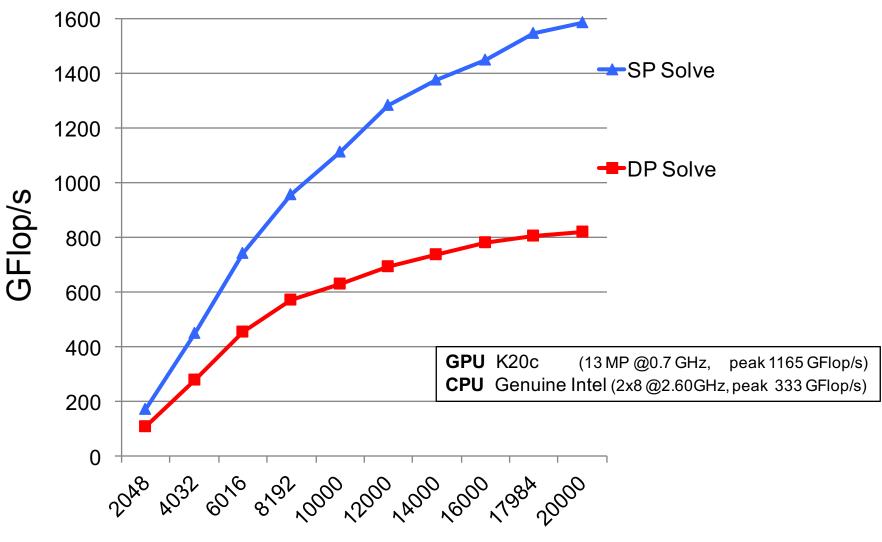

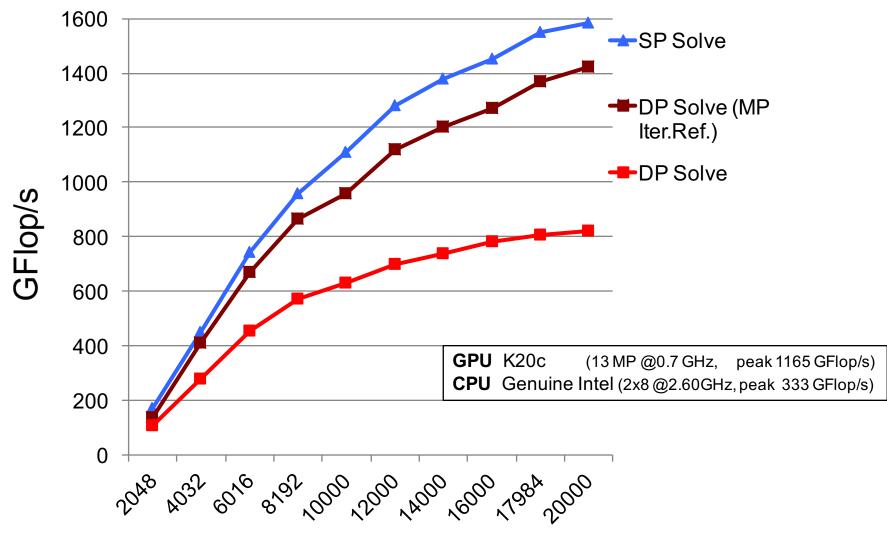

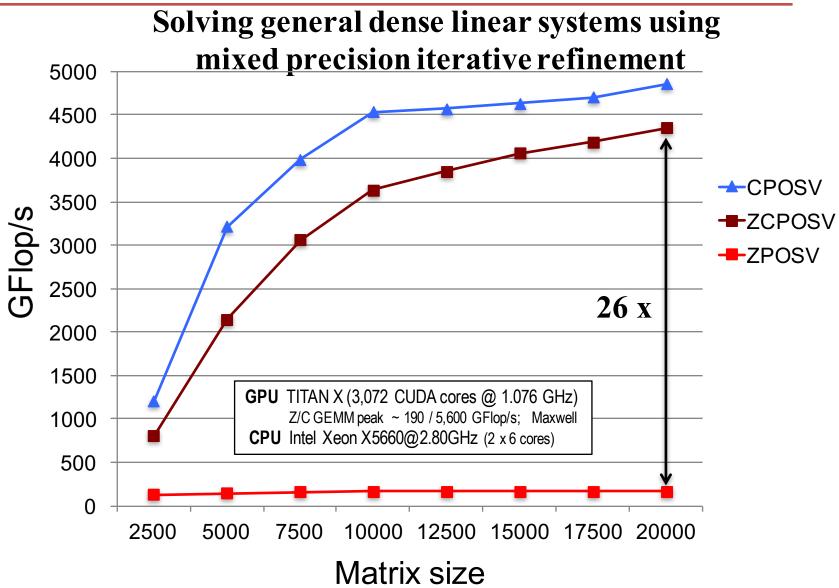

### Mixed precision iterative refinement

Solving general dense linear systems using mixed precision iterative refinement

Matrix size

Using same number of flops used for each implementation.

### Mixed precision iterative refinement

Solving general dense linear systems using mixed precision iterative refinement

Matrix size

Using same number of flops used for each implementation.

### Mixed precision iterative refinement

Using same number of flops used for each implementation.

### Critical Issues at Peta & Exascale for Algorithm and Software Design

- Synchronization-reducing algorithms

- Break Fork-Join model

- Communication-reducing algorithms

- Use methods which have lower bound on communication

- Mixed precision methods

- 2x speed of ops and 2x speed for data movement

- Autotuning

- Today's machines are too complicated, build "smarts" into software to adapt to the hardware

- Fault resilient algorithms

- Implement algorithms that can recover from failures/bit flips

- Reproducibility of results

- Today we can't guarantee this. We understand the issues, but some of our "colleagues" have a hard time with this.

# Summary

- Major Challenges are ahead for extreme computing

- Parallelism O(10<sup>9</sup>)

- Programming issues

- Hybrid

- Peak and HPL may be very misleading

- No where near close to peak for most apps

- Fault Tolerance

- Sequoia BG/Q node failure rate is 1.25 failures/day

- Power

- 50 Gflops/w (today at 2 Gflops/w)

- We will need completely new approaches and technologies to reach the Exascale level